# Design of very low voltage CMOS rectifier circuits

Adilson Jair Cardoso adilson.jair.cardoso @gmail.com Márcio Cherem Schneider

Carlos Galup Montoro carlosgalup@gmail.com

Federal University of Santa Catarina Florianópolis, Brazil

Abstract— This paper presents a simple analytical model of the basic rectifier circuit for very low voltage operation based on the Shockley (exponential) law of the diode. The main alternatives for the implementation of diodes in CMOS technologies and the calculation of the equivalent diode parameters for low voltage operation are summarized. The model of the half-wave rectifier for very low voltage is verified with measurements on a circuit built with a 1N4148 diode. The main diode implementations using MOS transistors of a 0.13  $\mu$ m technology operating in weak inversion are analyzed and a very simple design procedure is suggested.

## I. INTRODUCTION

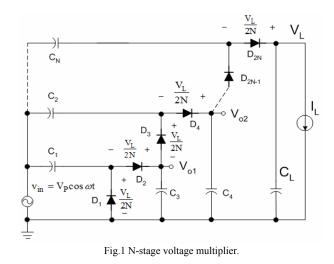

The demand for rectifier circuits that can efficiently operate at very low voltages is increasing as a consequence of the growing interest for RFID tag chips [1]. Low-voltage rectifiers are also used to process energy harvested from vibrations [2] or even from the body movement [3]. The use of energy harvesting has also been considered for biomedical devices [3]. In many energy harvesting devices, a rectifier circuit generates the dc voltage from a received ac or rf voltage. Since in these applications the ac voltages are usually not larger than a few hundred milivolts, a voltage multiplier circuit (Fig. 1) is used to obtain a dc voltage of the order of 1V.

#### **II. PREVIOUS WORK**

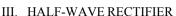

In our previous work [2] we designed voltage multipliers using MOS transistors operating as diodes in the AMIS 0.5  $\mu$ m and AMS 0.35 $\mu$ m technologies. Tests on the fabricated chips indicated requirements of minimum input voltage of 400m V<sub>peak</sub> and 150 mV<sub>peak</sub> for the chips in the AMIS 0.5 $\mu$ m and AMS0 0.35 $\mu$ m, respectively. Since there is no available analytical model for the rectifier operating at very low voltage, our previous designs were obtained after the simulation of many alternatives. The industrial need for a useful exploration of the available design space for low voltage rectifiers motivates the present work. Since the design of the voltage multiplier of Fig. 1 can be reduced to the design of the half wave rectifier of Fig. 2 [1] we will in the following focus on the performance of the topology of Fig. 2.

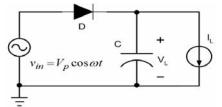

Fig. 3 illustrates the steady-state operation of the half wave rectifier of Fig. 2 for an input peak voltage *Vp* of 600 mV.

Fig. 2 Half-wave rectifier circuit with a dc current load.

In Fig. 3a the load voltage is nearly constant and, as a consequence, the peak diode current occurs simultaneously with the peak input voltage. In Fig. 3b and 3c, the ripple voltage  $\Delta V$  and the phase difference between the peaks of input voltage and diode current  $\Delta \phi$ , which depend on the load current, are shown. For the low voltage operation illustrated in Fig. 3, a constant voltage drop model of the diode is clearly inappropriate, and we must use the Shockley (exponential) diode model:

$$i_D = I_S \cdot \left( e^{\frac{v_D}{n \cdot \phi_i}} - 1 \right) \tag{1}$$

$$v_D = V_P \cdot \cos(\omega \cdot t) - V_L \tag{2}$$

where  $I_S$  is the diode saturation current,  $\phi_t$  is the thermal voltage, *n* is slope factor and  $V_L$  is the load voltage.

<sup>\*</sup>This work was supported by CNPq - Brazil.

Fig. 3 Input and output voltage and diode current of the rectifier of Fig. 2 for (a)  $I_L$ = 200 nA, (b)  $I_L$ =1µA, (c)  $I_L$ =4µA. The diode parameters are  $I_S$  = 4.4 nA and  $n \phi_t$  =45 mV, C=150nF, f=120Hz,  $\Delta$ Vcalc. (fig.3b) = 46mV,  $\Delta$ Vcalc. (fig.3c) = 182mV.

To calculate the DC current  $I_L$ , we integrate (1) over one period.

The dc component of the diode current equals the load current  $I_L$  thus using (1) and (2) we have

$$\frac{1}{T} \cdot \int_{0}^{T} i_{D} \cdot dt = \frac{1}{2\pi} \int_{-\pi}^{\pi} I_{S} e^{(V_{P} \cos \theta - V_{L})/n\phi_{I}} d\theta - I_{S} = I_{L}$$

(3)

Assuming that  $V_P > n \phi_t$ , the parabolic approximation of  $\cos\theta$  around zero and, consequently, the approximation of the diode current as a function of  $\theta$  by the normal function are fair approximations as we will verify in the following. Thus, we approximate the diode current as

$$i_D \cong I_S(e^{(V_P - V_L)/n\phi_t}e^{-V_P \theta^2/2n\phi_t} - 1)$$

(4)

Assuming a well filtered output,  $V_L$  can be taken as constant, thus, the substitution of (4) into (3) leads to [4]

$$I_{L} \cong \frac{1}{2\pi} \int_{-\infty}^{+\infty} i_{D} d\theta = I_{S} \left( \sqrt{\frac{n\phi_{t}}{2\pi V_{p}}} e^{\frac{V_{p} - V_{L}}{n\phi_{t}}} - 1 \right)$$

(5)

The analytical expression in (5) is equivalent to the use of the asymptotic expression below for the calculation of the zero order modified Bessel function  $B_0(x)$  [5],

$$B_0(x) \cong \frac{e^x}{\sqrt{2\pi x}} \tag{6}$$

$$x = \frac{V_P}{n \cdot \phi_t} \tag{7}$$

For x > 3, the error in (6) is below 5% [5].

Finally, from (5) we calculate the dc load voltage as

$$V_{L} = V_{P} - n\phi_{t} \ln \left[ \sqrt{\frac{2 \cdot \pi \cdot V_{P}}{n \cdot \phi_{t}}} \left( 1 + \frac{I_{L}}{I_{S}} \right) \right]$$

(8)

In (8), the second (logarithmic) term, which substitutes the constant  $V_{on}$  term of the conventional rectifier model, represents the maximum voltage drop on the diode.

The peak value of the diode current calculated from (4) and (8) is

$$I_{P} = I_{S} e^{\frac{V_{P} - V_{L}}{n \cdot \phi_{t}}} \cong I_{L} \sqrt{\frac{2 \pi V_{P}}{n \phi_{t}}}$$

(9)

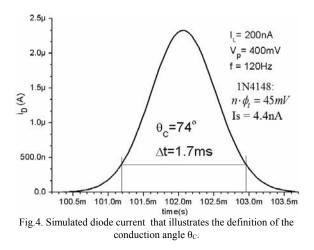

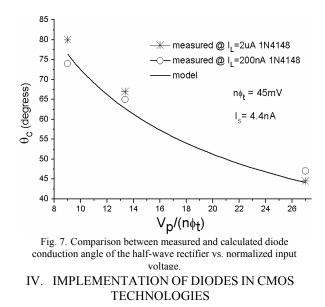

Finally, defining the conduction angle of the diode as that for which the charge that flows through the diode is 95% of the total charge in a cycle (Fig. 4) and using the normal function approximation for the diode current (4), we find that

$$\theta_C = 4\sigma = 4\sqrt{\frac{n\phi_i}{V_P}} \tag{10}$$

Thus, the conduction angle depends only on the  $V_P/\phi_t$  ratio. Once we have found the conduction angle, the voltage ripple  $\Delta V$ , shown in Fig. 3b and 3c, can be calculated as

$$\Delta V \cong \frac{I_L T}{C} \left( 1 - \frac{\theta_C}{2\pi} \right) \tag{11}$$

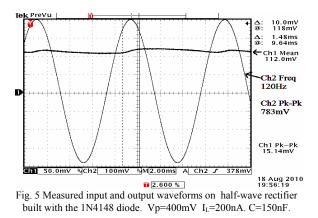

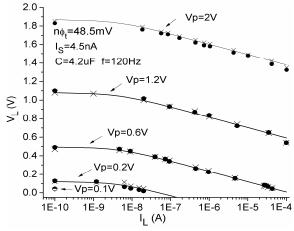

Results of measurements of the half-wave rectifier using a diode 1N4148 are shown in Figs. 5 - 7 and in Table I.

In Fig. 6 we can observe the fair fitting of eq. (8) for the ouput voltage of the rectifier with the 1N4148 diode for low values of the input voltage and for a wide range of output currents. Fig. 7 shows that the conduction angle is insensitive to load current. Finally, in Table I we summarize the comparison between experimental data and analytical model for  $I_L=200nA$ .

TABLE I COMPARISON BETWEEN MEASUREMENTS AND CALCULATION ON THE HALF WAVE RECTIFIER FOR IL=200nA.

|                            | Vp = 0.4V | Vp = 0.6V | Vp = 1.2V |

|----------------------------|-----------|-----------|-----------|

| VL calc. (8)               | 133mV     | 324mV     | 908mV     |

| VL meas.                   | 112mV     | 340mV     | 906mV     |

| v <sub>DMAX</sub> calc.(8) | 266mV     | 276mV     | 291mV     |

| v <sub>DMAX</sub> meas.    | 284mV     | 310mV     | 311mV     |

| Ip calc.(9)                | 1.6µA     | 1.9µA     | 2.6µA     |

| Ip meas.                   | 1.5µA     | 1.8µA     | 2.5µA     |

| $\theta c calc.(10)$       | 77°       | 63°       | 44°       |

| θc meas.                   | 74°       | 65°       | 47°       |

Fig. 6.Comparison between measured and calculated output voltage V<sub>L</sub> of the half-wave rectifier vs. load current

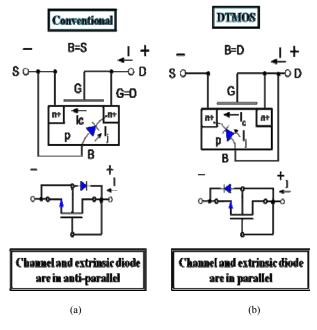

Figure 8 shows the two possible topologies for the MOS transistor connected as a diode. It is important to note that the diode current is composed by the channel current plus the current of the extrinsic diode. The disadvantage of the MOS transistor in the usual connection, with the bulk (B) tied to the source (S) (Fig. 8a), is the high reverse current. In effect, the reverse current of the device in Fig. 8a is due to the direct current in the extrinsic diode which increases exponentially with the increase of the magnitude of the reverse bias. To avoid the high reverse current of the conventional MOS diode, the DTMOS (Dynamic Threshold voltage MOSFET). connection can be used. In effect, in the DTMOS connection of the MOSFET, with the gate (G) tied to the substrate (Fig. 8b), the channel and the extrinsic diode are in parallel. The DTMOS connection can be used for p channel transistors in an n-well process or for the nMOS transistors in p- or triple-well processes. To model the MOS diodes, we will use, for the sake of simplicity, the weak inversion model, which is appropriate for low voltage operation.

The drain to source current is expressed [6] by:

$$I_{DS} = \frac{W}{L} I_o e^{\frac{V_{GB} - V_{TO}}{n \cdot \phi_l}} \left[ e^{\frac{-V_{SB}}{\phi_l}} - e^{\frac{-V_{DB}}{\phi_l}} \right]$$

(12)

$$I_O = \mu_0 n C'_{ox} \phi_l^2 e^1$$

(13)

where  $\mu_0$  is the carrier mobility,  $C_{ox}$  the oxide capacitance per unit area, W/L the transistor aspect ratio, *n* the transistor slope factor and  $V_{TO}$  the threshold voltage.

Fig. 8. The two possible connections of a MOS transistor as a diode.

For the DTMOS connection of Fig. 8b, we have from (12)

$$I_D = \frac{W}{L} I_o \cdot e^{\frac{-V_{TO}}{n \cdot \phi_t}} \left[ e^{\frac{v}{\phi_t}} - 1 \right]$$

(14)

where  $v = -V_{SB}$  and the saturation current  $I_S$  of the implemented diode is given by

$$I_{s} = \frac{W}{L} I_{o} \cdot e^{\frac{-V_{TO}}{n \cdot \phi_{l}}}$$

(15)

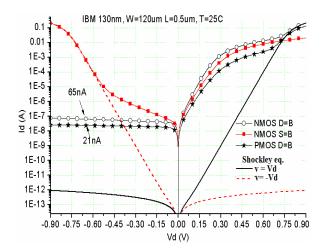

Since for the DMOS  $V_{GB} = V_{DB} = 0$ , the DTMOS diode behaves as an ideal diode with ideality factor n = 1 for low voltage (weak inversion) operation, as shown in (14). It is interesting to observe that the  $I_S$  current in (14) corresponds to the saturated drain current of the transistor with  $V_{GS} = V_{SB} = 0$ . As is clear from (15), to obtain a diode with high  $I_S$  saturation current, for efficient low voltage operation, we must use a technology with a low  $V_{TO}$  and design the adequate geometric factor W/L. Finally, the simulated characteristics of some of the diode structures available in a 0.13 µm technology are shown in Fig. 9.

Fig 9 I-V characteristics for some diode connected transistors in a 0.13 μm technology Junction Diode: nφt=37mV

### V. SUMARY

A simple analytical model for the low voltage rectifier was presented. Equation (8) allows determining the minimum peak input voltage for a given diode and load requirements. Conversely, the knowledge of the input voltage allows determining the diode I-V characteristics for the load requirements. We have also shown that the conduction angle of the diode is independent of the load current. The analytical model, when used with data extracted from the simulated characteristics of MOSFET diodes, allows the rapid exploration of the design space of low voltage rectifiers in CMOS technologies. In its simplest form the design consists of the two following steps: first, determine  $I_S$  from the rectifier requirements using (8); second, calculate the transistor aspect ratio from (15).

#### REFERENCES

- J.-P. Curty, N. Joehl, F. Krummenacher, C. Dehollain and M. Declercq, "A model for μ-power rectifier analysis and design," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 52. no. 12, pp. 2771-2779, Dec. 2005.

- [2] A. J. Cardoso, C. G. Montoro and M.C. Schneider. "CMOS Rectifier Design for Energy Harvesting based on Vibrations," XV Wokshop IBERCHIP, Iguaçu Falls, Brazil, 2010, pp.241-245.

- [3] R. Amirtharaj, P. Wright, "Energy Harvesting for Biomedical Devices and Health Care Intelligent Infrastructure", available at http://www.citris-uc.org/research/projects/energy\_harvesting\_for\_bio medical\_devices\_and\_health\_care\_intelligent\_infrastructure

- [4] P. C. Dunn, *Gateways Into Electronics*. John Wiley and Sons, New York, 2000.

- [5] M. Abramowitz and I. S. Stegun, *Handbook of Mathematical Functions*, Dover Publications, New York, 1970.

- [6] E. Vittoz and J. Fellrath, "CMOS analog circuits based on weak inversion operation," *IEEE J. Solid State Circuits*, vol. 12, no. 3, pp. 224-231, June 1977.